8.14.1 Overview of CPU Socket Constraints

8.14.1 Overview of CPU Socket Constraints

CPU socket constraints enable you to create and configure a logical domain, which owns limited virtual CPUs, cores, or memory, with the specified CPU socket ID. Since the CPU socket ID is associated with the LSB number and CPU location number, you can fully control the hardware resources manually without using physical bindings, such as CID and PA.

The CPU socket ID is determined by the LSB number and CPU location number as follows.

| CPU socket ID = LSB number x 4 + CPU location number |

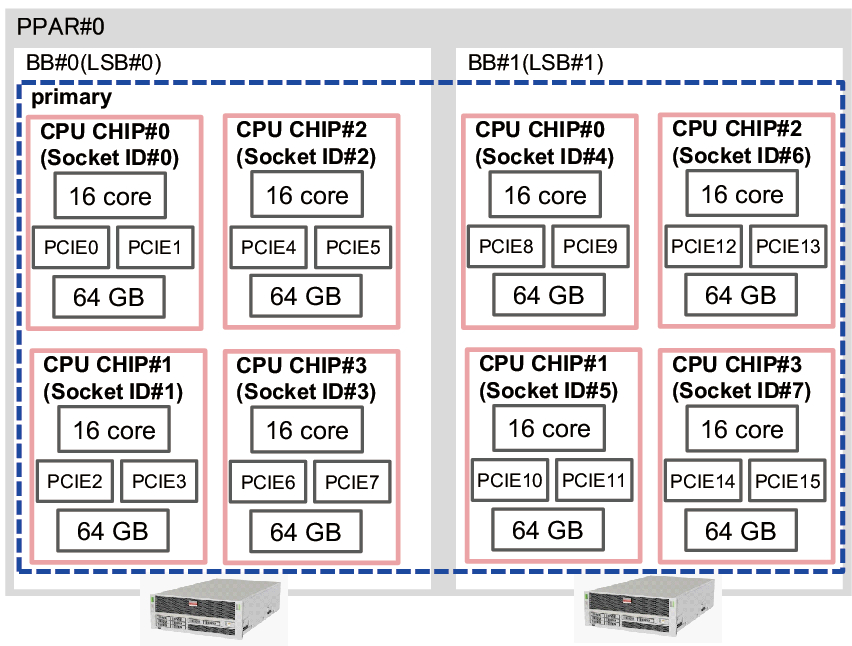

Figure 8-1 shows the physical resources in the physical partition configured with two SPARC M10-4S units (BB#0 and BB#1).

|

Figure 8-1 Resources in a Physical Partition

|

|

For details on the LSB number and CPU location number, see "2.4.1 Consideration of Logical Domain Configuration" in the Fujitsu SPARC M12 and Fujitsu M10/SPARC M10 Domain Configuration Guide.

You can use the CPU socket constraints to perform tasks like the following.

- Create a highly reliable domain by using memory mirroring enabled on the specified CPU chip

- Before executing the dynamic reconfiguration (PPAR DR) of a physical partition, separate the SPARC M12-2S and SPARC M10-4S resources to be deleted in advance to minimize the time that a guest domain, on which PPAR DR is being executed, is stopped.

- Tune the performance by spreading the virtual CPUs to each CPU chip or by consolidating the virtual CPUs in one CPU chip.

- Configure a logical domain using only the SPARC64 X+ processor in a physical partition that also has the SPARC M10-4S with the SPARC64 X/SPARC64 X+ processor.

The following commands are provided as CPU socket constraint-related commands. For details on each command, see the Oracle VM Server for SPARC Reference Manual of the version used.

- ldm list-socket

- ldm set-socket

- ldm grow-socket

- ldm shrink-socket

< Previous Page | Next Page >